一、实验内容

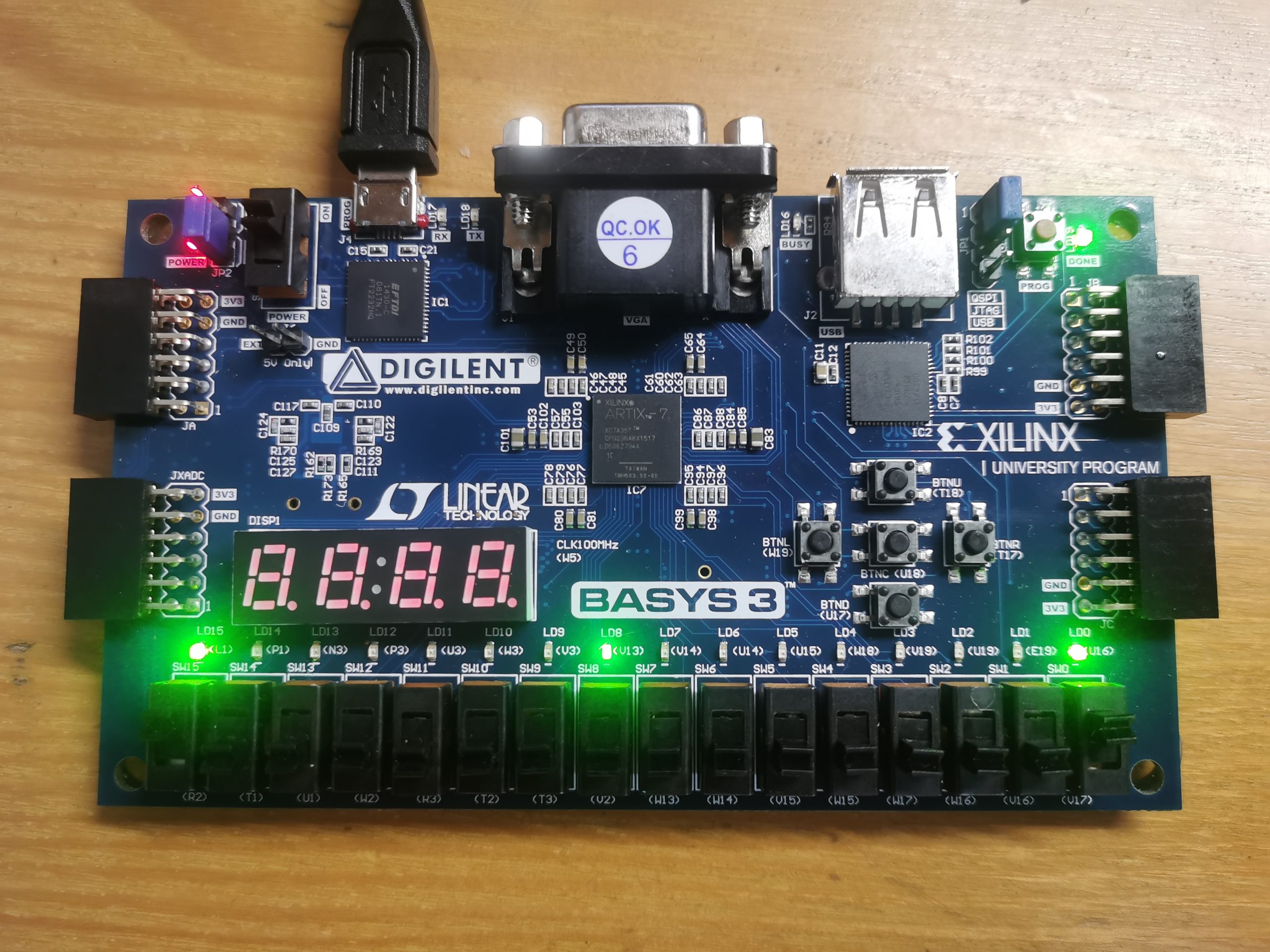

用 HDL 描述是否踢球裁决器的逻辑功能,并在 BASYS3 开发板上实现验证。

判断准则为:如果不下雨,且有空,则去踢球。否则就不去踢球。其中:

SW15=1 表示晴天,SW15=0 表示下雨。LED15 反映对应的 SW15 高低。

SW0 =1 表示有空,SW0 =0 表示没空。LED0 反映对应的 SW0 高低。

LED8 亮表示去踢球,否则表示不去踢球。

二、实验方案

LED0,LED15 分别由 SW0,SW15 直接控制;

利用与门控制 LED8,当 SW0,SW15 均输出高电平时 LED8 点亮

三、实验分析

- mainDesign.sv(代码文件)

module mainDesign(

input logic SW0,

output logic LED0,

input logic SW15,

output logic LED15,

output logic LED8

); //定义端口

assign LED0 = SW0;

assign LED15 = SW15;

assign LED8 = (SW0 & SW15);//赋值运算

endmodule2.Basys3_Master.xdc(约束文件)

## Switches

set_property PACKAGE_PIN V17 [get_ports {SW0}]

set_property IOSTANDARD LVCMOS33 [get_ports {SW0}]

set_property PACKAGE_PIN V2 [get_ports {SW8}]

set_property IOSTANDARD LVCMOS33 [get_ports {SW[8}]

set_property PACKAGE_PIN R2 [get_ports {SW15}]

set_property IOSTANDARD LVCMOS33 [get_ports {SW15}]

## LEDs

set_property PACKAGE_PIN U16 [get_ports {LED0}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED0}]

set_property PACKAGE_PIN V13 [get_ports {LED8}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED8}]

set_property PACKAGE_PIN L1 [get_ports {LED15}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED15}]四、实验结果

1.输入:SW0=0 SW15=0 输出:LED0=0 LED15=0 LED8=0(没空下雨不踢球)

2.输入:SW0=1 SW15=0 输出:LED0=1 LED15=0 LED8=0(有空下雨不踢球)

3.输入:SW0=0 SW15=1 输出:LED0=0 LED15=1 LED8=0(没空晴天不踢球)4.输入:SW0=1 SW15=1 输出:LED0=1 LED15=1 LED8=1(有空晴天去踢球)

有空晴天去踢球

五、总结与思考

1.Verilog 在大小写上高度敏感,Basys3_Master.xdc 默认的均采用 led,sw 等小写

字母,如果和代码文件 SW,LED 不一致的话在编译程序时会报错。

2.在定义端口的时候要检查有没有漏!即便未定义端口在编译程序时不会报

错,但是实际运行时不会产生任何输入/输出值。

3.编写 Verilog 程序时还是需要注意基本的语法规范。

4.收获:Vivado 的安装与使用,Verilog 基本语法,简单的逻辑运算。

111